计算机组成原理考点

第一章 计算机系统概述¶

- 计算机硬件组成要素 :哪些部分?功能是什么

- 运算器: 算术与逻辑运算

- 存储器: 存储指令和数据

- 控制器: 执行指令/协调各部件工作

- 总线: 连接各个部件的公共通路

- 输入、输出设备与适配器: 信息转换/与用户交互

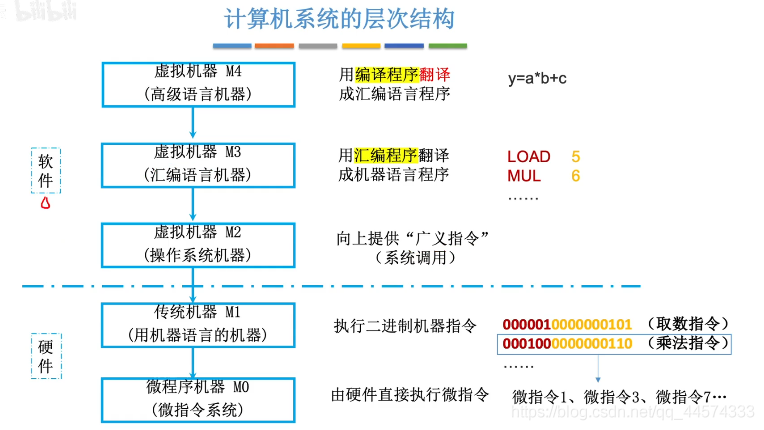

- 计算机系统的层次结构:以语言为特点

- 高级语言机器 M4(软件): 用编译程序翻译成汇编语言程序

- 汇编语言机器 M3(软件): 用汇编程序翻译成机器语言程序

- 操作系统机器 M2(软件): 向上提供“广义指令”(系统调用)

- 用机器语言的机器 M1(硬件): 执行二进制机器指令

- 微程序机器 M0(硬件)由硬件直接执行微指令

第二章 数据的表示与运算(运算器)¶

- 不同进制数的转换

- 数的机器码: 原、反、补、移码的表示范围(表示形式与对应的真值)

- 原、反码表示范围相同;补、移码表示范围相同,比原、反多表示一个最小负数(

1 0000/0 00000)

- 原、反码表示范围相同;补、移码表示范围相同,比原、反多表示一个最小负数(

- 定点数的表示: 纯整数、纯小数, 表示范围

- 注意规格化尾数 最大负数(绝对值最小) 只能取到

1 000...0001

-

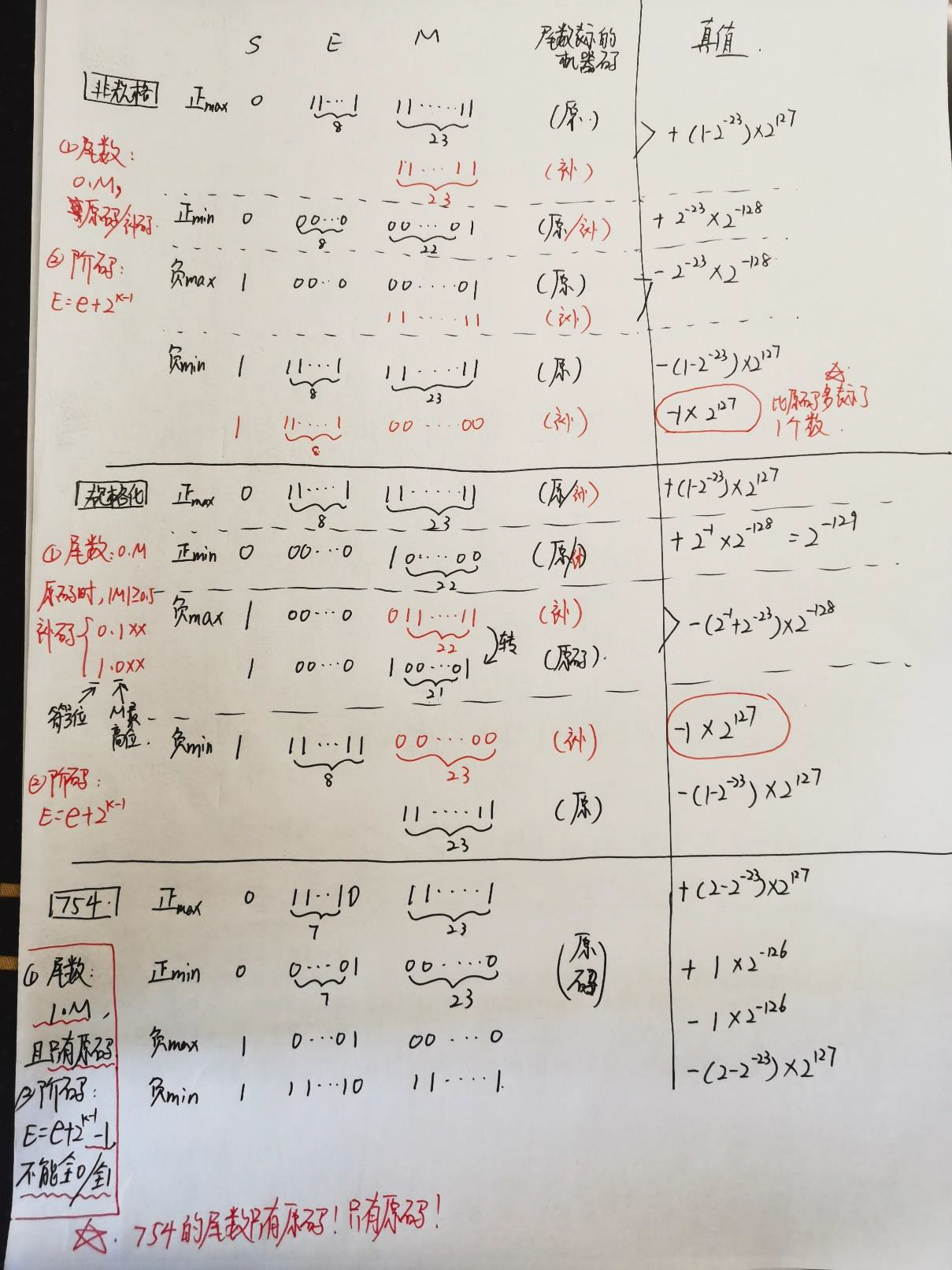

浮点数的表示: 非规格化、规格化 、 IEEE754 标准 (特定的规格化格式)

- 不同形式的特点,存储格式、表示范围、 真值

-

定点数(补码表示)的加减法运算:基本规则、 溢出判断

- -y 的补码、 变形补码的表示

- 定点数 的乘法:基本规则、 乘法阵列包含器件数量

- 定点数 除法 :基本规则、 不恢复余数除法计算

- n 位加法器的设计原理

- 级联形成 n 位加法器(行波进位加法器) 的特点

- 先行进位的基本原理;先行进位 n 位加法器的特点

- 74181 和 74182 的外部特性、如何形成 ALU

- 浮点数加、减法运算: 运算流程 、各阶段特点

- 对阶, 尾数加减, 规格化, 舍入, 溢出

- 流水线定义与特点:同步时钟控制

第三章 存储器¶

- 存储器的组成 :存储元、存储单元、地址

- 存储元: 存储器中最小的物理单元, 保存一个二进制位

- 存储单元: 由若干个存储元组成;每个存储单元占用 1 个地址

- 地址: 标识存储单元所在的位置

- 不同方式下的存储器的分类;

- 分级存储体系的特点; 存储容量、寻址范围(地址数量) 计算

- SRAM 存储器的特点; SRAM 的基本组成部分;读 写周期分析

- DRAM 存储器的特点( VS. SRAM);DRAM 的基本结构; DRAM 的刷新

- 集中刷新, 分散刷新,异步刷新

- 存储器的设计(容量扩充) 【必考】

- 并行存储器的工作原理、特点:双端口存储器、多模交叉存储器(带宽)

- 设置 Cache 的原理与目标、 Cache 的评价指标

- 主存与 Cache 的地址映射 不同方式下主存、 Cache 的地址格式;行标记容量;映像关系

- 全相联,直接映射,组相联

第四章 指令系统¶

-

指令系统的基本概念:指令、指令系统

- 指令:指示计算机执行某种操作的命令(微指令、机器指令、宏指令)

- 指令系统:一台计算机所有机器指令的集合。(CISC、RISC)

-

指令的格式:操作码、地址码(多种情况); 格式分析 、指令编码

- 操作码:不可变长度、可变长度

- 地址码:零地址、一地址(隐含指定)、二地址、三地址

- 格式分析:RR、RS、SS

- 指令的寻址方式

- 顺序寻址(PC+1)

- 跳跃寻址(JMP)

- 数据的寻址方式 : 不同寻址方式下,有效地址的计算方式;数据实际存储位置

- 隐含寻址、立即寻址

D = A、直接寻址D=(A)、间接寻址D=((A)) - 寄存器寻址

D=(Ri)、寄存器间接寻址D=((Ri)) - 偏移寻址

EA=A+(R)- 相对寻址(相对于 PC, 即 PC=R)

- 基址寻址(基址 R 变,A 不变)

- 变址寻址(基址 R 不变,A 变)

- 隐含寻址、立即寻址

第五章 CPU¶

- CPU 的基本组成:各部分的功能与特点

- 运算器:实现数据的算术和逻辑运算 (ALU、ACC、PSW、CT、寄存器组、移位器)

- 控制器:产生控制信号, 协调和指挥各个部件完成执行指令的操作(PC、IR、指令译码器、(M)AR、(M)DR、时序系统、微操作信号发生器)

- cache:存储指令和数据

- 指令周期、 CPU 周期与时钟周期的关系

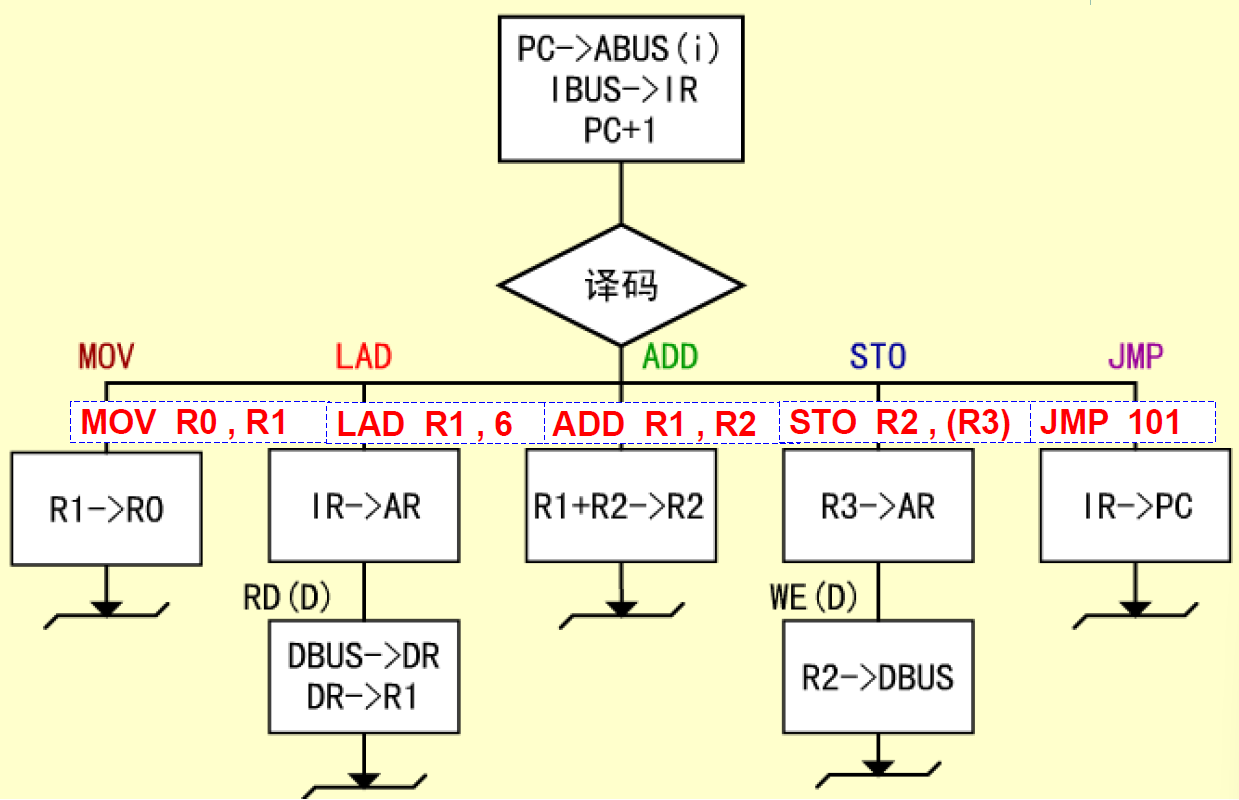

- 指令周期: CPU 从内存取出一条指令并执行这条指令的所有操作时间总和 。(如 ADD、SUB、LAD、MOV 等)

- 一个指令周期 又可细分成 若干个 CPU 周期

- CPU 周期: 又称机器周期(机器指令周期),一般用 从内存读取一条指令字 的最短时间来定义。

- 一个 CPU 周期 又包含 若干时钟周期

- 时钟周期: CPU 处理操作的基本时间单位,通常称为 节拍脉冲 或 T 周期

- CPU 中最小的时间单位,时钟周期越短(时钟频率越高)说明计算机工作速度越快

- 指令周期: CPU 从内存取出一条指令并执行这条指令的所有操作时间总和 。(如 ADD、SUB、LAD、MOV 等)

- 指令周期分析 : 方框语言描述指令周期流程图

- 注意测试必须占一个 CPU 周期, 若后续无 CPU 周期, 添加一个空的 CPU 周期

- 时序产生器的功能;控制方式

- 时序产生器: 生成各种时序信号,控制计算机中各个部件的协调工作

- 时序信号:控制不同部件之间的时间协调,保证计算机系统的正常工作

- 控制方式

- 同步控制方式: 指令在执行时所需的机器周期数 (CPU 周期)和时钟周期数(节拍脉冲)都固定不变

- 异步控制方式: 指每个操作控制信号根据需要确定完成时间

- 联合控制方式: 同步控制和异步控制相结合的方式

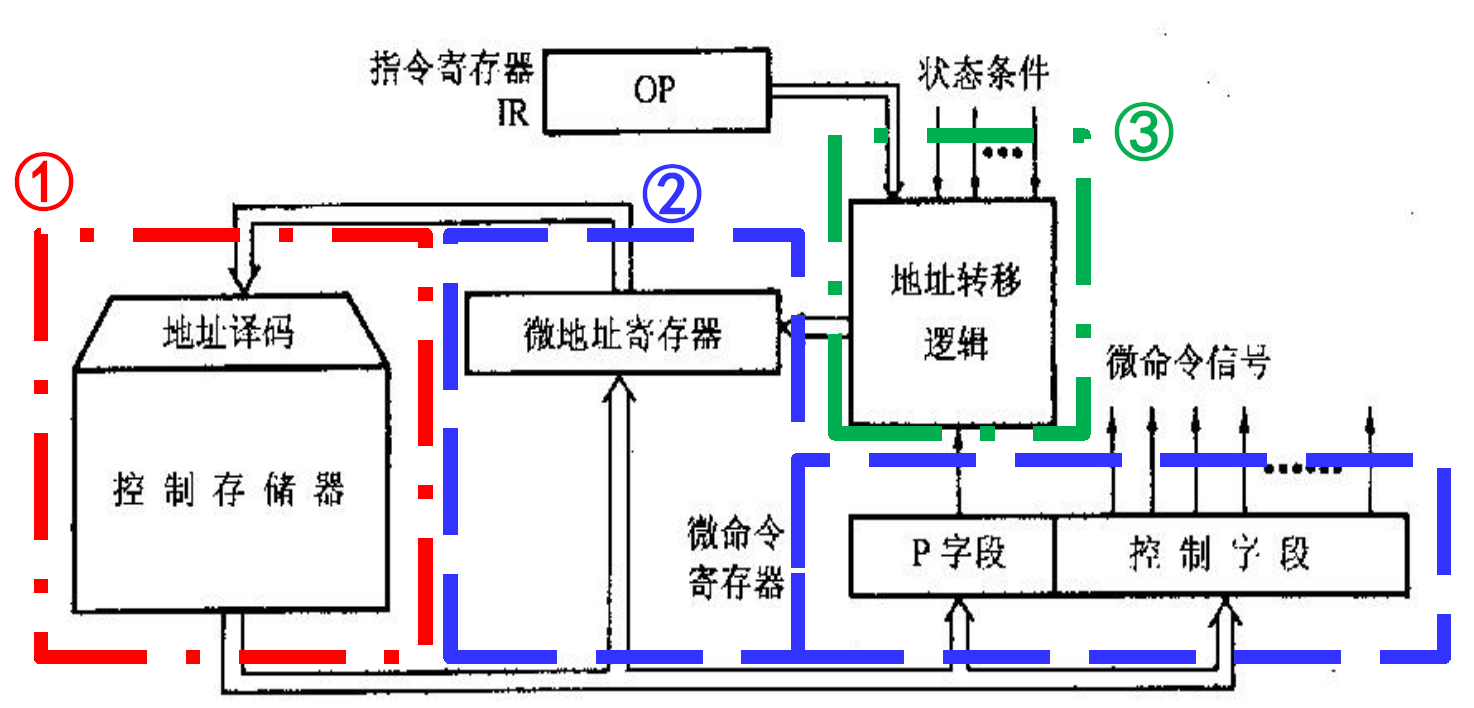

- 微程序控制器的工作原理 : 控制的核心思想;基本组成部分、各部分功能与关系

- 核心思想: 将机器指令执行过程分为若干个微操作,并通过预先设计和存储在 ROM(只读存储器)中的微程序来控制这些微操作的执行顺序和时序,从而实现对整个计算机系统中各个部件的协调控制

- ①控制存储器 CM: 用于存放实现全部指令系统的微程序 (用 ROM 制造)

- ②微指令寄存器 μIR: 用来存放当前执行的一条微指令 (分段存放)

- 微命令寄存器: 存放 P 字段+操作控制字段

- 微地址寄存器 μAR: 顺序控制字段

- ③地址转移逻辑: 用于形成下条微指令的微地址

- 微程序的设计

- 微命令编码技术;微地址形成方式(微地址转移逻辑的设计)

- 1 条指令的微程序设计 (根据指定的数据通路图,完成某一特定功能的指令的程序)

- 硬连线控制器的工作原理( Vs. 微程序控制器

- 使用门电路和触发器构成的逻辑电路来产生控制信号

- 流水线的相关:不同的相关类型;数据相关的判断

- 资源相关、数据相关(WAR、RAW、RAR)、控制相关

第六章 总线系统¶

- 单总线、多总线结构的特点

- 单总线:系统内的所有部件均由同一条总线(系统总线) 连接,进行数据传输和控制信号传递

- 多总线:将计算机系统中的总线分为数据总线、地址总线和控制总线等多条总线,用于传输不同类型的信息

- 总线带宽的计算:单位时间内通过总线的数据位数(MB/s)

- 总线接口的定义、作用

- 接口: CPU 和主存、外设之间通过总线进行连接的逻辑部件

- 作用: 控制、缓冲、状态、转换、整理、程序中断等。

- 总线的仲裁:仲裁的目的、仲裁策略、 仲裁的不同实现方式及其特点

- 目的: 多个功能模块争用总线时,必须由总线仲裁部件选择一个主设备使用总线

- 集中式仲裁: 由总线控制部件进行仲裁

- 链式查询方式(菊花链)

- 计时器定时查询方式

- 独立请求方式

- 分布式仲裁: 不需要中央仲裁器,每个潜在的主模块都有自己的仲裁器和仲裁号,多个仲裁器竞争使用总线

- 总线信息传送过程 ( 5 个阶段)

- 请求总线、总线仲裁、寻址、信息传送、状态返回

- 总线的定时方式:同步、异步;分析周期图

- 同步定时: 系统采用统一的时钟信号 ,所有事件的出现时间均由该时钟信号确定

- 异步定时: 系统依靠应答方式或互锁机制 来决定事件出现的时间

第七章 外围设备¶

- 外围设备:定义、 基本组成要素 、常见的外设及其分类

- 定义:计算机系统(主机)与外界交换信息的装置

- 基本组成 :

- 存储介质: 用于信息的保存;

- 驱动装置: 用于移动存储介质,使之正常工作;

- 控制电路: 用于使该外设与外界(如 CPU)的信息传递。

- 分类

- 输入输出设备;

- 外存设备;

- 数据通信设备;

- 过程控制设备

- 硬磁盘存储器的特点:读写原理(简要)、硬盘组成结构、 信息分布、地址表示

- 写:磁头写线圈脉冲电流,磁化存储元;读:磁头读线圈将存储元的剩磁状态转换为电信号读出

- 组成: 磁记录介质、磁盘控制器、磁盘驱动器

- 纪录面、磁道、圆柱面、扇区

- 地址:磁道号(柱面号)、记录面号(磁头号)、扇区号

- 硬磁盘的技术指标计算 : 存储容量(格式化、非格式化)、存取时间

- \(\textcolor{#66ccff}{非格式容量}=最大位密度 \times 最内圈磁道周长 \times 总磁道数\)

- \(\textcolor{#66ccff}{格式化容量}=每道扇区数 \times 扇区容量 \times 总磁道数\)

- \(\textcolor{#66ccff}{T_a=T_s+\frac 1{2r}+\frac b{rN}}\) 寻道时间+平均等待时间+数据传送时间

- 显示设备的基本概念 :像素、分辨率、灰度级或颜色数、刷新存储器及其容量、带宽的计算

- 像素: 构成图像的基本单位。

- 分辨率: 显示器能表示的像素个数。

- 灰度级: 像素明暗差别的程度。

- 颜色数: 显示器能显示的颜色的种类。

- 刷新存储器: 存放图像信息用于刷新的存储器,也叫 显示存储器;

- 容量:M = r x C (r: 分辨率, C:灰度级)

第八章 输入输出¶

- 接口的定义

- 为 CPU 和主存、 I/O 设备之间传送信息而设的转换逻辑部件。

- I/O 设备与 CPU 交换信息的过程

- 输入过程:

- CPU 送地址选择某一输入设备;

- CPU 等候数据成为有效

- CPU 读入数据, 存入相应的寄存器中。

- 输出过程:

- CPU 送地址选择某一输出设备;

- CPU 把数据放在数据总线上;

- 输出设备取数据。

- 输入过程:

- 主机与外设信息交换方式概述 :哪两类?具体 4 种方式

- 程序实现

- 程序查询方式

- 程序中断方式

- 硬件实现

- DMA 方式

- 通道方式

- 程序实现

- 程序查询方式特点:设备编址方式、接口电路结构、工作流程

- 编址方式

- 与存储器统一编址: 在存储器总的地址空间中分出一个区域,作为 I/O 系统中的设备地址。

- 独立编址:内存与外围设备地址各自独立。

- 接口电路

- 设备选择电路

- 数据缓冲寄存器

- 设备状态标志电路

- 编址方式

- 程序中断方式 :基本概念、中断处理过程的流程、接口电路结构

- 当有某些 随机事件 发生时 CPU 暂停执行当前的程序 ,转去执行引起中断的程序 ,处理完后再 返回继续执行原程序

- 中断请求 → 中断响应 → 中断服务

- 单级中断 VS 多级中断: 多级中断下,如何通过修改屏蔽字改变中断处理优先级

- DMA 方式:基本思想、一般处理流程、不同的传送方式

- 通过硬件控制总线实现主存与 I/O 设备间的直接数据传送, 在传送过程中无需 CPU 程序干预

- 流程

- DMA 请求: 外设通过接口向 CPU 发 DMA 请求信号。

- DMA 响应: CPU 将工作改为 DMA 操作方式,将总线控制权交给 DMA 控制器。

- DMA 数据传送: DMA 控制器发总线信号,在主存和 I/O 寄存器之间传送数据。

- 结束处理: 数据传送完后,发结束中断请求 ,通知 CPU 进行后处理。

- 传送方式

- CPU 与 DMA 控制器控制内存方式

- 停止 CPU 访问内存

- DMA 与 CPU 交替访存

- 周期挪用

- CPU 与 DMA 控制器控制内存方式

- 通道方式:基本思想

- 通道:一种专用处理器 ,通过执行通道程序进行 I/O 操作的管理,为主机与 I/O 设备提供数据传送通道。